# 7185 MANUAL

5 channel RS-422 + 4 channel encoder interface

This page intentionally almost blank

# **Table of Contents**

| GENERAL                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| DESCRIPTION                                                                                                                                    |

| HARDWARE CONFIGURATION                                                                                                                         |

| DEFAULT CONFIGURATION                                                                                                                          |

| CONNECTORS                                                                                                                                     |

| CONNECTOR LOCATIONS AND DEFAULT JUMPERS CONTROLLER CONNECTOR 5V POWER ENCODER CONNECTOR TB3 ENCODER /SERIAL CONNECTOR TB2 SERIAL CONNECTOR TB1 |

| OPERATION                                                                                                                                      |

| 5V POWER                                                                                                                                       |

| SPECIFICATIONS                                                                                                                                 |

### **GENERAL**

#### **DESCRIPTION**

The 7I85 is a five channel RS-422 serial plus four channel encoder interface for Mesa's 25 pin Anything I/O series of FPGA interface cards. The 7I85 is designed for motion control applications. A common usage of the 7I85 would be connecting up to four serially interfaced drives to four of the 7I85s five full duplex RS-422 interfaces and up to four encoders with index to the 7I85s encoder inputs.

Encoder inputs can be TTL or differential on a per input basis. The 7l85 can also supply 5V power to encoders. A 7l85S version is available that replaces the five serial interfaces with 10 differential ouputs that can be used as five differential step+ dir output pairs or PWM outputs or other output functions.

The controller connection is a DB25 connector that matches the pinout of Mesa's 25 pin Anything I/O cards. All buffered I/O is terminated with 3.5 mm pluggable screw terminals (supplied)

### HARDWARE CONFIGURATION

#### **GENERAL**

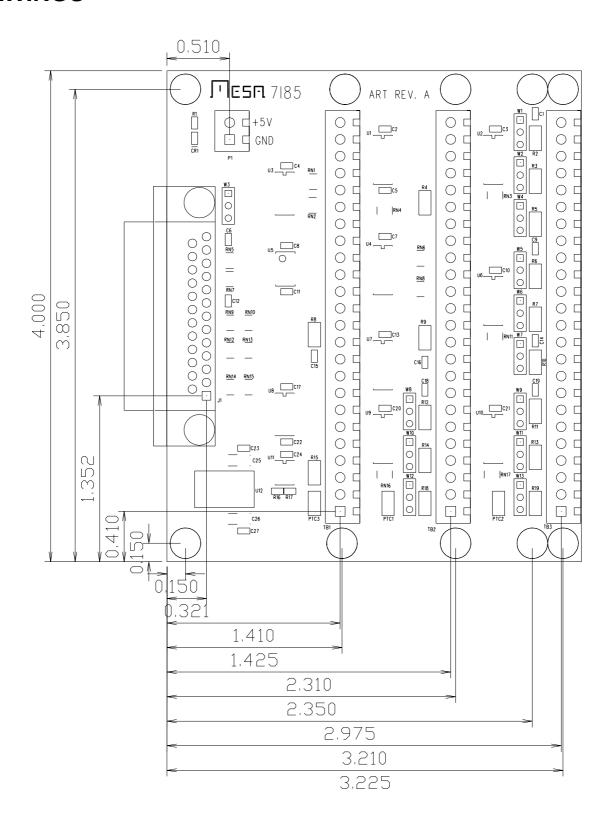

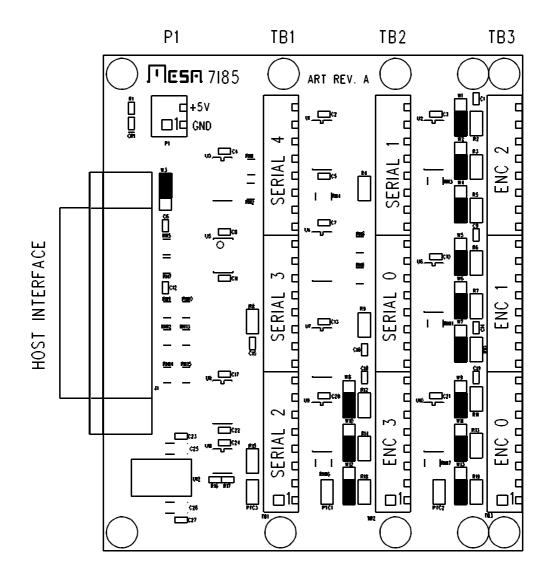

Hardware setup jumper positions assume that the 7185 card is oriented in an upright position, that is, with the 50 pin controller connector is on the left hand side.

#### **DEFAULT CONFIGURATION**

| FUNCTION           | DEFAULT SETTING                                           |

|--------------------|-----------------------------------------------------------|

| CABLE/AUX 5V POWER | UP = CABLE 5V POWER                                       |

| ENCODER 0          | ALL DOWN = RS-422                                         |

| ENCODER 1          | ALL DOWN = RS-422                                         |

| ENCODER 2          | ALL DOWN = RS-422                                         |

| ENCODER 3          | ALL DOWN = RS-422                                         |

|                    | CABLE/AUX 5V POWER<br>ENCODER 0<br>ENCODER 1<br>ENCODER 2 |

#### TTL/RS-422 ENCODER SELECTION

Each 7I85 encoder channel has a selectable TTL or RS-422 (differential) encoder input conditioning. Conditioning type is determined by setting groups of 3 jumpers to the up or down position. When the jumpers are in the "UP" position, TTL inputs are selected, When the jumpers are in the "DOWN" position, RS-422 inputs are selected. Note these sets of three jumpers are in physical proximity to the terminal block encoder connections.

#### **CABLE POWER**

The 7I85 can get its logic power from the host FPGA card or from P1. W3 determines if the 7I85 gets its 5V logic power from the host FPGA card or P1.

If W3 is in the 'UP' position, host FPGA power is used and the host FPGA card must be jumpered to supply 5V to the daughtercard.

If W3 is in the 'DOWN' position, 5V power must be supplied to the 7l85 via P1 and the 7l85 grounds the 4 DB25 signals used for host 5V power. In this case the FPGA card must be jumpered so that it does **not** supply power to the daughtercard.

### **CONNECTOR LOCATIONS AND DEFAULT JUMPER POSITIONS**

Note: TB1,TB2,TB3 Pin 1 is marked with square and '1'

### **CONTROLLER CONNECTOR**

Female 25 pin DB-25F P1 is the host interface connector. This connects to the host interface FPGA card via a IEEE-1284 male-male DB-25 cable.

| DB-25 PIN | FPGA PRIM I/O | FPGA SEC I/O | FUNCTION |

|-----------|---------------|--------------|----------|

| 1         | IO0           | IO17         | RX4      |

| 14        | IO1           | IO18         | TX4      |

| 2         | IO2           | IO19         | RX3      |

| 15        | IO3           | IO20         | TX3      |

| 3         | IO4           | IO21         | RX2      |

| 16        | IO5           | IO22         | TX2      |

| 4         | 106           | IO23         | RX1      |

| 17        | 107           | IO24         | TX1      |

| 5         | IO8           | IO25         | RX0      |

| 6         | IO9           | IO26         | TX0      |

| 7         | IO10          | IO27         | ENCMUX   |

| 8         | IO11          | IO28         | MENCA0   |

| 9         | IO12          | IO29         | MENCB0   |

| 10        | IO13          | IO30         | MIDX0    |

| 11        | IO14          | IO31         | MENCA1   |

| 12        | IO15          | IO32         | MENCB1   |

| 13        | IO16          | IO33         | MIDX1    |

Pins 18, 19, 20, and 21 are ground. Pins 22, 23, 24 and 25 are either ground or 5V depending on jumper W1 (ground if W1 "DOWN", 5V if W1 "UP").

### **5V POWER**

2 pin pluggable terminal P1 can be used to supply 5V power to the I/O terminals on the7l85. This is suggested for applications where the encoders or remote serial cards draw more current than can be supplied via the host interface cable. P1 has the following pinout:

# PIN FUNCTION

1 GND

2 +5V

### **ENCODER CONNECTOR TB3**

Connector TB3 is a 3.5MM pluggable screw terminal block with encoder channels 0 through 2:

| TB3 PIN | FUNCTION | DIR       |

|---------|----------|-----------|

| 1       | QA0      | TO 7185   |

| 2       | /QA0     | TO 7185   |

| 3       | GND      | FROM 7185 |

| 4       | QB0      | TO 7185   |

| 5       | /QB0     | TO 7185   |

| 6       | +5V      | FROM 7185 |

| 7       | IDX0     | TO 7185   |

| 8       | /IDX0    | TO 7185   |

| 9       | QA1      | TO 7185   |

| 10      | /QA1     | TO 7185   |

| 11      | GND      | FROM 7185 |

| 12      | QB1      | TO 7185   |

| 13      | /QB1     | TO 7185   |

| 14      | +5V      | FROM 7185 |

| 15      | IDX1     | TO 7185   |

| 16      | /IDX1    | TO 7185   |

| 17      | QA2      | TO 7185   |

| 18      | /QA2     | TO 7185   |

| 19      | GND      | FROM 7185 |

| 20      | QB2      | TO 7185   |

| 21      | /QB2     | TO 7185   |

| 22      | +5V      | FROM 7185 |

| 23      | IDX2     | TO 7185   |

| 24      | /IDX2    | TO 7185   |

Note that actual signal functions depend on FPGA configuration.

### **ENCODER/SERIAL CONNECTOR TB2**

Connector TB2 is a 3.5MM pluggable screw terminal block with the following pinout:

| TB2 PIN FUNCTION |       | DIR       |  |

|------------------|-------|-----------|--|

| 1                | QA3   | TO 7185   |  |

| 2                | /QA3  | TO 7185   |  |

| 3                | GND   | FROM 7185 |  |

| 4                | QB3   | TO 7185   |  |

| 5                | /QB3  | TO 7185   |  |

| 6                | +5V   | FROM 7185 |  |

| 7                | IDX3  | TO 7185   |  |

| 8                | /IDX3 | TO 7185   |  |

| 9                | GND   | FROM 7185 |  |

| 10               | GND   | FROM 7185 |  |

| 11               | RX0   | TO 7185   |  |

| 12               | /RX0  | TO 7185   |  |

| 13               | TX0   | FROM 7185 |  |

| 14               | /TX0  | FROM 7185 |  |

| 15               | +5V   | FROM 7185 |  |

| 16               | +5V   | FROM 7185 |  |

| 17               | GND   | FROM 7185 |  |

| 18               | GND   | FROM 7185 |  |

| 19               | RX1   | TO 7185   |  |

| 20               | /RX1  | TO 7185   |  |

| 21               | TX1   | FROM 7185 |  |

| 22               | /TX1  | FROM 7185 |  |

| 23               | +5V   | FROM 7185 |  |

| 24               | +5V   | FROM 7I85 |  |

Note that actual signal functions depend on FPGA configuration.

### **SERIAL CONNECTOR TB1**

Connector TB1 is a 3.5MM pluggable screw terminal block with the following pinout:

| TB1 PIN | FUNCTION | DIR       |

|---------|----------|-----------|

| 1       | GND      | FROM 7185 |

| 2       | GND      | FROM 7185 |

| 3       | RX2      | TO 7185   |

| 4       | /RX2     | TO 7185   |

| 5       | TX2      | FROM 7185 |

| 6       | /TX2     | FROM 7185 |

| 7       | +5V      | FROM 7185 |

| 8       | +5V      | FROM 7185 |

| 9       | GND      | FROM 7185 |

| 10      | GND      | FROM 7185 |

| 11      | RX3      | TO 7185   |

| 12      | /RX3     | TO 7185   |

| 13      | TX3      | FROM 7185 |

| 14      | /TX3     | FROM 7I85 |

| 15      | +5V      | FROM 7I85 |

| 16      | +5V      | FROM 7185 |

| 17      | GND      | FROM 7185 |

| 18      | GND      | FROM 7185 |

| 19      | RX4      | TO 7185   |

| 20      | /RX4     | TO 7185   |

| 21      | TX4      | FROM 7185 |

| 22      | /TX4     | FROM 7185 |

| 23      | +5V      | FROM 7185 |

| 24      | +5V      | FROM 7185 |

Note that actual signal functions depend on FPGA configuration.

### **OPERATION**

#### **5V POWER**

The 7I85 requires ~200 mA of 5V power for operation. This power will increase based on the number of terminated TX outputs used, up to a maximum of ~300 mA of local logic power. Encoder power and remote serial device power must be added to this figure for total power draw

Power for the 7l85 logic is normally supplied from the host interface but can also be supplied via P1, the 5V power connector.

The 5V power to I/O connectors TB1, TB2, and TB3 each pass through a 1.1A PTC device before being routed to the I/O terminals. This limits the I/O power supplied by TB1, TB2, and TB3 to  $\sim$ 640 mA each in 0 to 70C ambients.

#### **ENCODER INPUT CIRCUIT**

The 7l85 input circuit is different depending on whether TTL or RS-422 encoder types have been selected. In TTL mode the input circuit on the encoder QA, QB, and IDX inputs drive one input of the RS-422 differential receiver, and the other receiver input is terminated to a 1.6V (TTL threshold) reference voltage. In RS-422 mode, the input consists of a 120 Ohm termination resistor and a 26LS32 RS-422 differential receiver.

When TTL encoders are used, they connect to the 'True' input of the differential pair, for example a TTL encoder for channel 2 would connect to QA2, QB2 and IDX2, while the /QA2, /QB2, and /IDX2 terminals would be left open.

Fine print: normally the input mode jumpers would always be moved as a sets of three to select TTL or RS-422 mode for individual encoders, however it is possible to select TTL or RS-422 mode for each encoder signal, for example if a encoder had a differential A, B but TTL index, the input circuit can accommodate this. The three input mode select jumpers are in bottom to top order: QA, QB, IDX.

### **OPERATION**

#### MAXIMUM ENCODER COUNT RATE

The 7l85 uses multiplexed encoder signals to save interface pins. The multiplexing rate will determine the maximum encoder count rate. Default multiplexing rate with HostMot2 firmware is ClockLow / 8,or approximately 4 or 6 MHz, giving a resolvable count rate of 2 to 3 MHz. Multiplexing rate can be increased if desired but high multiplex rates will require short cables between the FPGA controller card and the 7l85 due to signal integrity and time-of-flight considerations. Maximum practical multiplex rate is approximately 12 MHz (and 6 MHz count rates). Encoder count rate is further limited by HostMot2s input filtering to ~5 to ~8 million counts per second (encoder filtering off) and ~1 to ~1.6 million counts per second (encoder filtering on).

#### INTERFACING WITH MESA SERIAL DEVICES

The 7I85 is intended to be a general purpose RS-422 serial plus encoder interface but can easily interface to MESA's SSerial I/O devices that use RS-422 communication and RJ45/CAT5 cable for the serial interface. These devices include the 7I64 Isolated I/O interface, the 8I20 3 phase drive, the 7I66 isolated I/O interface, the 7I69 TTL I/O interface and the 7I73 pendant interface. The easiest way to make a cable for interfacing the 7I85 to these devices is to take a standard CAT5 or CAT6 cable, cut it in half, and wire the individual wires to the 7I85 screw terminals. The following chart gives the CAT5 to 7I85 screw terminal connections (EIA/TIA 568B colors shown):

| 7185 PIN | 7185 SIGNAL | DIRECTION | CAT5 PIN | CAT5 568B COLOR |

|----------|-------------|-----------|----------|-----------------|

| 1,9,17   | GND         | FROM 7185 | 4        | BLUE            |

| 2,10,18  | GND         | FROM 7185 | 5        | BLUE / WHITE    |

| 3,11,19  | RX+         | TO 7185   | 6        | GREEN           |

| 4,12,20  | RX-         | TO 7185   | 3        | GREEN / WHITE   |

| 5,13,21  | TX+         | FROM 7185 | 2        | ORANGE          |

| 6,14,22  | TX-         | FROM 7185 | 1        | ORANGE / WHITE  |

| 7,15,23  | +5V         | FROM 7185 | 7        | BROWN / WHITE   |

| 8,16,24  | +5V         | FROM 7I85 | 8        | BROWN           |

# **SPECIFICATIONS**

|                                               | MIN     | MAX  | UNITS    |

|-----------------------------------------------|---------|------|----------|

| 5V POWER SUPPLY                               | 4.75    | 5.25 | VDC      |

| 5V POWER CONSUMPTION                          |         | 300  | mA       |

| (all outputs loaded with 130 ohm terminations | s)      |      |          |

| (no external encoder or serial 5V load)       |         |      |          |

| 5V CURRENT TO EACH I/O CONNECTOR              |         | 640  | mA       |

| MAXIMUM DATA RATE                             |         | 10   | MBIT/S   |

| RS-422 INPUT COMMON MODE RANGE                | -7      | +12  | Volts    |

| RS-422 TERMINATION RESISTANCE                 | 118     | 122  | Ohm      |

| RS-422 OUTPUT LOW                             | _       | .8   | Volts    |

| (24 mA sink current)                          |         |      |          |

| RS-422 OUTPUT HIGH                            | VCC-2.5 | _    | Volts    |

| (24 mA source current)                        |         |      |          |

| ENC INPUT COMMON MODE RANGE                   | -7      | +12  | Volts    |

| ENC INPUT TTL MODE THRESHOLD                  | 1.4     | 1.8  | Volts    |

| OPERATING TEMP.                               | 0       | +70  | °C       |

| OPERATING TEMP. (-I version)                  | -40     | +85  | °C       |

| OPERATION HUMIDITY                            | 0       | 95%  | NON-COND |

# **DRAWINGS**